# Technical Challenges of Exascale Computing

Contact: Dan McMorrow — dmcmorrow@mitre.org

April 2013

JSR-12-310

Approved for public release; distribution unlimited.

JASON The MITRE Corporation 7515 Colshire Drive McLean, Virginia 22102-7508 (703) 983-6997

# Contents

| 1 | ABSTRACT<br>EXECUTIVE SUMMARY                 |                                                 |    |  |  |

|---|-----------------------------------------------|-------------------------------------------------|----|--|--|

| 2 |                                               |                                                 |    |  |  |

|   | 2.1                                           | Overview                                        | 4  |  |  |

|   | 2.2                                           | Findings                                        | 7  |  |  |

|   | 2.3                                           | Recommendations                                 | 9  |  |  |

| 3 | DOE/                                          | 'NNSA COMPUTING CHALLENGES                      | 11 |  |  |

|   | 3.1                                           | Study Charge from DOE/NNSA                      | 11 |  |  |

|   | 3.2                                           | Projected Configuration of an Exascale Computer | 13 |  |  |

|   | 3.3                                           | Overview of DOE Exascale Computing Initiative   | 15 |  |  |

|   | 3.4 ′                                         | The 2008 DARPA Study                            | 17 |  |  |

|   | 3.5                                           | Overview of the Report                          | 19 |  |  |

| 4 | HARDWARE CHALLENGES FOR EXASCALE COMPUTING 2  |                                                 |    |  |  |

|   | 4.1                                           | Evolution of Moore's Law                        | 21 |  |  |

|   | 4.2                                           | Evolution of Memory Size and Memory Bandwidth   | 25 |  |  |

|   | 4.3                                           | Memory Access Patterns of DOE/NNSA Applications | 32 |  |  |

|   | 4.4 ′                                         | The Roof-Line Model                             | 39 |  |  |

|   | 4.5                                           | Energy Costs of Computation                     | 46 |  |  |

|   | 4.6                                           | Memory Bandwidth and Energy                     | 48 |  |  |

|   | 4.7                                           | Some Point Designs for Exascale Computers       | 50 |  |  |

|   |                                               | Resilience                                      | 52 |  |  |

|   | 4.9                                           | Storage                                         | 57 |  |  |

|   | 4                                             | 4.9.1 Density                                   | 58 |  |  |

|   | 4                                             | 4.9.2 Power                                     | 60 |  |  |

|   | 4                                             | 4.9.3 Storage system reliability                | 67 |  |  |

|   | 4.10                                          | Summary and Conclusions                         | 71 |  |  |

| 5 | <b>REQUIREMENTS FOR DOE/NNSA APPLICATIONS</b> |                                                 |    |  |  |

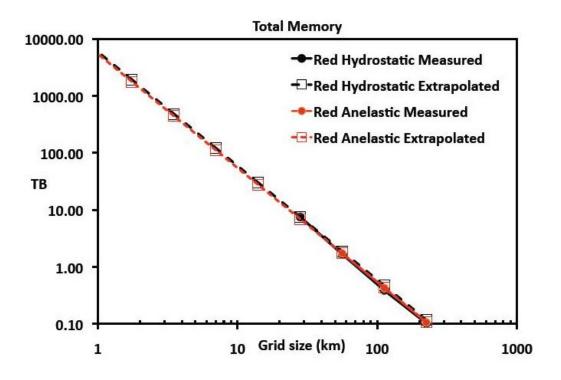

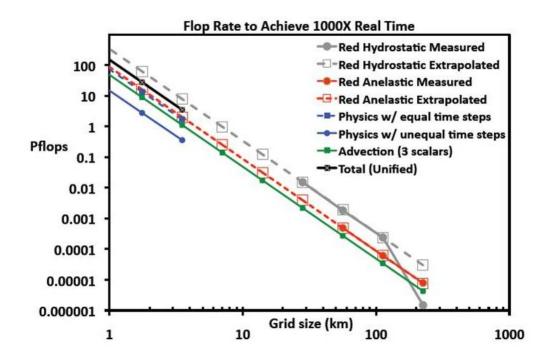

|   | 5.1                                           | Climate Simulation                              | 73 |  |  |

|   |                                               | Combustion                                      | 78 |  |  |

|   |                                               | NNSA Applications                               | 89 |  |  |

|   |                                               | Summary and Conclusion                          | 90 |  |  |

| 6 | <b>RESEARCH DIRECTIONS</b>                 |                                                              |     |

|---|--------------------------------------------|--------------------------------------------------------------|-----|

|   | 6.1                                        | Breaking the Memory Wall                                     | 93  |

|   | 6.2                                        | Role of Photonics for Exascale Computing                     | 96  |

|   | 6.3                                        | Computation and Communication Patterns of DOE/NNSA Appli-    |     |

|   |                                            | cations                                                      | 99  |

|   | 6.4                                        | Optimizing Hardware for Computational Patterns               | 103 |

| 7 | SOF                                        | TWARE CHALLENGES                                             | 107 |

|   | 7.1                                        | Domain Specific Compilers and Languages                      | 108 |

|   | 7.2                                        | Auto-Tuners                                                  | 110 |

|   | 7.3                                        | Summary and Conclusion                                       | 112 |

| 8 | REC                                        | COMMENDATIONS FOR THE FUTURE                                 | 115 |

|   | 8.1                                        | Co-Design                                                    | 115 |

|   | 8.2                                        | The Need for an Intermediate Hardware Target                 |     |

|   | 8.3                                        | Summary                                                      | 119 |

|   | 8.4                                        | Recommendations                                              | 119 |

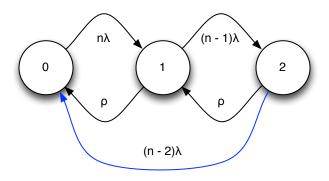

| A | APF                                        | PENDIX: Markov Models of Disk Reliability                    | 123 |

| B | APF                                        | <b>PENDIX: Uncertainty Quantification for Large Problems</b> | 129 |

| С | APPENDIX: NNSA Application Requirements 13 |                                                              |     |

| D | APF                                        | PENDIX: Briefers                                             | 137 |

## **1 ABSTRACT**

JASON was tasked by DOE/NNSA to examine the technical challenges associated with exascale computing. This study examines the issues associated with implementing DOE/NNSA computational requirements on emerging exascale architectures. The study also examines the national security implications of failure to execute a DOE Exascale Computing Initiative in the 2020 time frame.

### **2 EXECUTIVE SUMMARY**

The past thirty years have seen an exponential increase in computational capability that has made high performance computing (HPC) an important enabling technology for research and development in both the scientific and national security realms. In 2008, computational capability as measured by the LINPACK linear algebra benchmark reached the level of 10<sup>15</sup> floating point operations per second (a petaflop). This represents a factor of 1000 increase in capability over the teraflop level (10<sup>12</sup> floating point operations per second) achieved in 1997. JA-SON was tasked by the DOE Office of Science and the ASC Program of NNSA to examine the technical challenges associated with exascale computing, that is, developing scientific and national security applications using computers that provide another factor of 1000 increase in capability in the 2020 time frame. DOE/NNSA posed the following questions to JASON:

- 1. What are the technical issues associated with mapping various types of applications with differing computation and communication platforms to future exascale architectures, and what are the technical challenges to building hardware that can respond to different application requirements?

- 2. In the past programming tools have been afterthoughts for high performance platforms. What are the challenges in designing such tools that can also be gracefully evolved as the hardware evolves?

- 3. What are the economic and national security impacts of failure to execute the DOE Exascale Computing Initiative (ECI)? What application capabilities will emerge in the absence of an initiative?

JASON's assessment of these issues is summarized below and in a more detailed form in the main report.

#### 2.1 Overview

While petascale computing was largely achieved through an evolutionary refinement of microprocessor technology, the achievement of exascale computing will require significant improvements in memory density, memory bandwidth and perhaps most critically, the energy costs of computation.

Much of the impressive increase in computing capability is associated with Moore's law, the observation that the number of transistors on a processor has increased exponentially with a doubling time of roughly 18 months, as well as Dennard scaling which allowed for increases in processor clock speed. However, as of 2004, for a variety of technical reasons discussed in this report and elsewhere, serial performance of microprocessors has flattened. Clock speeds, for the most part, now hover around 2–6 gigaherz and there is no expectation that they will increase in the near future. The number of transistors continues to increase as per Moore's law, but modern microprocessors are now laid out as parallel processors with multiple processing cores. It is projected that to achieve an exaflop (10<sup>18</sup> floating point operations per second), an application developer will need to expose and manage 1 billion separate threads of control in their applications, an unprecedented level of parallelism.

At the same time, while the number of cores is increasing, the amount of total memory relative to the potential floating point capability is decreasing. This is largely due to the fact that memory density has not increased as quickly as floating point capability, with the result that maintaining the ratio of memory capacity to floating point capability is becoming prohibitively expensive. Today, this is viewed as a matter of cost, but it will eventually limit the working set size of computations and underscores the need for new memory technologies that offer higher density. In addition, memory access times have decreased over time, but not as quickly as floating point capability has increased. These issues are wellknown to processor architects as the "memory wall".

Perhaps the most significant challenge for exascale computing is bounding the energy required for computation. DOE/NNSA has set a power budget for an exascale platform at roughly 20 megawatts. This is a typical power load for a modern large data center. Each picoJoule per second (a picowatt) expended by the hardware in communication or computation translates into 1 megawatt of required power at the exascale. For example, a computation requiring the delivery of an exaword of memory (10<sup>18</sup> 64 bit words) per second (that is the delivery of one word for every floating point operation) would consume 1.3 gigawatts of power using today's processors and memory. Although advances in device and circuit design will continue, by 2020 this number is expected to only decrease to 320 megawatts.

If these trends regarding memory size, memory bandwidth, and the associated energy costs continue to hold, two critical issues will emerge. First, it will only be possible to run applications that require a small working set size relative to computational volume. There are important DOE/NNSA applications that are in this class, but there are also a significant number that utilize working sets in excess of the projections for memory capacity of an exascale platform in the 2020 time frame. Second, only applications that can effectively cache the required memory will be able to run on an exascale platform within the required power envelope and also provide a reasonable percentage of peak computational throughput. At present, many DOE/NNSA applications, including some that will be used for future stockpile stewardship investigations, require significant memory bandwidth to perform efficiently. The projected memory limitations will make it impossible to increase the spatial or model fidelity of current implementations of DOE/NNSA applications at a level commensurate to the thousand-fold increase in floating point performance envisioned by 2020.

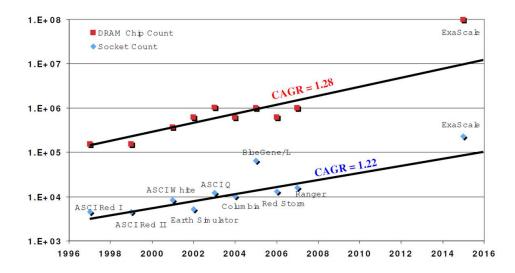

An additional challenge will be insuring that an exascale platform will function in the presence of hardware failures. This is known as resilience. It is projected that an exascale platform may have as many as  $10^8$  memory chips and  $10^5$  $-10^6$  processors. Data on resilience of high performance computers are relatively sparse. Without aggressive engineering however, crude projections show that such a machine will function without system interruption for merely tens of minutes.

The expected complexity of any future exascale platform as regards memory hierarchy, resilience, etc. will make it necessary to consider different approaches to software development. In the past, applications were largely written using explicit message passing directives to control execution in a way that was often very specific to the details of the hardware. Ideally, an application developer should make clear the type and amount of parallelism associated with a specific algorithm. The specific implementation on a given hardware platform should be left to a compiler aided by software that can optimize the generated code for maximal throughput. At present, compilers for traditional programming languages cannot infer such information without some specification of the underlying computation and communication patterns inherent in a particular algorithm. Promising research directions include domain-specific languages and compilers as well as auto-tuning software. A research effort is required to develop language constructs and tools to reason about massively parallel architectures in a way that does not explicitly require detailed control of the hardware. In any case, software for future exascale platforms cannot be an afterthought, and the level of investment in software technology must be commensurate with the level of investment in hardware.

In order to attempt to address these issues, DOE/NNSA have initiated a set of "co-design" centers. These centers are meant to facilitate the communication of scientific problem requirements to hardware designers and thus influence future hardware designs. In turn, designers communicate hardware constraints to application developers so as to guide the development of future algorithms and software. JASON is concerned however that, as currently practiced, co-design may fail to give DOE/NNSA the leverage it needs. More focus is required to ensure that the hardware and software under development will target improvements in the performance of the dominant patterns of computation relevant to DOE/NNSA applications. In particular, there is a need to enhance the level of communication so that a true exchange of ideas takes place. In some cases, intellectual property concerns make such exchanges very difficult. Resolution of these issues is required if these centers are to contribute effectively.

#### 2.2 Findings

Our findings regarding the technical challenges of exascale computing are as follows:

**Importance of leadership in HPC** US leadership in high performance computing is critical to many scientific, industrial and defense problems. In order to maintain this leadership, continued investment in HPC technology (both hardware and software) is required. It is important to note however, that maintenance of this leadership is not necessarily tied to the achievement of exascale computing capability by 2020. Such leadership can be maintained and advanced with ongoing investments in research and development that focus on the basic technical challenges of achieving balanced HPC architecture.

- **Feasibility of an exascale platform by 2020** It is likely that a platform that achieves an *exaflop* of peak performance could be built in a 6–10 year time frame within the DOE/NNSA designated power envelope of 20 megawatts. However, such a platform would have limited memory capacity and memory bandwidth; owing to these limitations such an exascale platform may not meet many DOE/NNSA application requirements.

- **National security impacts** To achieve DOE/NNSA mission needs, continued advances in computing capability are required and will be required for the foreseeable future. However, there is no particular threshold requirement for exascale capability in the 2020 time frame as regards those national security issues associated with the DOE/NNSA mission. For this reason, JASON does not foresee significant national security impacts associated with a failure to execute the DOE Exascale Computing Initiative by 2020.

- **Technical challenges** The most serious technical challenge impeding the development of exascale computing in the near term is the development of powerefficient architectures that provide sufficient memory density and bandwidth for DOE/NNSA applications.

- **Focus on DOE/NNSA application requirements** More focus is required to ensure that the hardware and software under development in support of an exascale capability will address performance improvements specific to the communication and computational patterns of DOE/NNSA applications.

- **Focus on software tools** More focus is also required to develop software that will facilitate development of and reasoning about applications on exascale platforms regardless of the details of the underlying parallel architecture.

- **Co-design strategy** The current co-design strategy is not optimally aligned with the goal of developing exascale capability responsive to DOE/NNSA application requirements. More focus is required to ensure that the hardware and software under development will target improvements in the performance of the dominant patterns of computation relevant to DOE/NNSA applications.

#### 2.3 **Recommendations**

Our recommendations are as follows:

- **Continued investment in exascale R&D is required** Rather than target the development of an exascale platform in the 2020 time frame, DOE/NNSA should invest in research and development of a variety of technologies geared toward solving the challenging issues currently impeding the development of balanced exascale architecture: increased memory density, memory bandwidth, energy-efficient computation, and resilience.

- **Establish intermediate platform targets** DOE/NNSA should establish a set of intermediate platform targets in pursuit of balanced HPC architecture over a realistic time frame. An attractive set of intermediate targets are platforms that provide *sustained* computational floating point performance of 1, 10, and ultimately 100 petaflops, but optimized for DOE/NNSA computational requirements, with memory capacity and bandwidth targets that exceed current microprocessor vendor road maps, and with a maximum power consumption of 5 megawatts or less. A variety of technical approaches should

be supported in meeting this target with eventual down-select of the most promising approaches.

- Assess application requirements Undertake a DOE/NNSA effort to characterize in a standard way the computational patterns and characteristics (i.e. memory capacity, memory bandwidth, floating point intensity and global communication ) of the suite of DOE/NNSA applications.

- **Enhance investment in software tools** Support development of software tools at a budgetary level commensurate with that provided for hardware development. In particular, support for tools like domain-specific languages and auto-tuning software is needed so that users can reason about programs in terms of scientific requirements as opposed to hardware idiosyncrasies.

- **Improve the co-design strategy** Enhance the current co-design strategy so that it not only focuses on the optimization of existing codes, but also encourages hardware and software innovation in direct support of the dominant patterns of computation relevant to DOE/NNSA applications.

### **3 DOE/NNSA COMPUTING CHALLENGES**

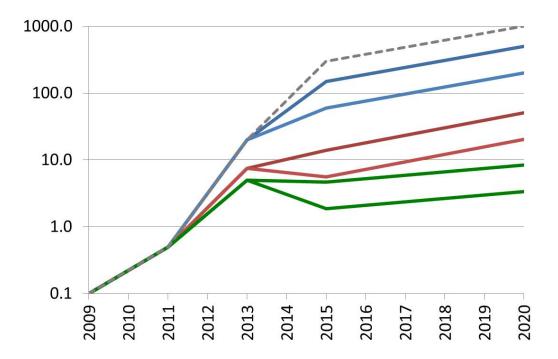

The past three decades have seen an exponential increase in computational capability that has made computing an essential part of the scientific enterprise. Shown in Figure 3-1 is the evolution of the number of floating point operations per second (flops) that can be achieved on a modern high performance computer. Two types of results are shown - the peak rate in which all functional units of the computer are active and the "maximum" rate that is measured using the LINPACK benchmark that measures the time it takes to factor a full  $N \times N$  matrix. It can be seen that, in 1993, peak speeds were on the order of  $10^{10}$  floating operations per second (flops) or tens of gigaflops. In 1997, through the development efforts of the NNSA ASC program, a capability to compute at  $10^{12}$  flops or a teraflop was demonstrated and ten years later, again via the efforts of the ASC program, a petaflop capability was demonstrated. What is perhaps more remarkable is that this increase was achieved largely by the development of increasingly capable microprocessors without a significant change in hardware architecture.

#### 3.1 Study Charge from DOE/NNSA

A logical question is whether this trend can continue to provide an additional factor of 1000 in the 2017 time frame - ten years from the development of computers capable of peak speeds approaching a petaflop or petascale computation. This next level -  $10^{18}$  floating point operations per second is known as exaflop or exascale computing. As will be detailed below, achieving this next level of capability will be very challenging for a number of reasons detailed in this report, and noted in many previous studies.

Figure 3-1: Evolution of peak performance over the period 1993 - 2009 [27]

DOE and the NNSA tasked JASON to study the possibility of developing an exaflop computational capability. We quote below from the study charge as communicated by DOE/NNSA to JASON:

"This study will address the technical challenges associated with the development of scientific and national security applications for exascale computing. The study will examine several key areas where technology development will be required in order to deploy exascale computing in the near future:

Applications: It is likely that a future exascale platform will utilize a hierarchical memory and network topology. As a result, there may be barriers to optimal performance for certain types of scientific applications. What are the technical issues associated with mapping various types of applications with differing computation and communication platforms to future exascale architectures, and what are the technical challenges to building hardware that can respond to different application requirements?

- 2. Programming environments: The development of application codes for future exascale platforms will require the ability to map various computations optimally onto a hierarchical computing fabric. In the past, programming tools have been after-thoughts for high performance platforms. What are the challenges in designing such tools that can also be gracefully e-volved as the hardware evolves?

- 3. What are the economic and national security impacts of failure to execute the DOE Exascale Computing Initiative (ECI)? What application capabilities will emerge in the absence of an initiative? "

#### **3.2** Projected Configuration of an Exascale Computer

The challenges in delivering a factor of 1000 over present day petascale computing are significant for several reasons. In Table 3.1, we list some of the requirements associated with exascale computing in relation to present day petascale computing. For reasons associated with powering and cooling of modern microprocessors, it is no longer possible to speed up processors by simply increasing the clock speed. This limitation is discussed further in Section 4. As a result, computational throughput is increased today by exposing parallel aspects of the program being executed and delegating the computation to individual processor cores. This is not a new development, and as shown in Table 3.1, today's petascale systems already use this "multi-core" approach. What will be different however, when considering exascale computing, is that because the clock speed cannot be easily increased, the

| Attribute             | Petascale (realized)           | Exascale target              |  |

|-----------------------|--------------------------------|------------------------------|--|

| Peak flops            | $2 \times 10^{15}$ flops       | $1 \times 10^{18}$ flops     |  |

| Memory                | 0.3 Petabyte                   | 50 Petabytes                 |  |

| Node performance      | $1.25 \times 10^{11}$ flops    | $2 \times 10^{12}$ flops     |  |

| Node memory bandwidth | $2.5 \times 10^{10}$ bytes/sec | $1 \times 10^{12}$ bytes/sec |  |

| Node concurrency      | 12 cores                       | 1000 cores                   |  |

| Number of nodes       | $2 \times 10^4$ nodes          | $1 \times 10^6$ nodes        |  |

| Total concurrency     | $2.25 \times 10^5$ threads     | $1 \times 10^9$ threads      |  |

Table 3.1: Attributes of an exascale computer

throughput per core is not expected to increase significantly and so the only way to increase throughput is to increase the number of cores on a node.

It is projected that one can realistically build systems with roughly  $10^5 - 10^6$  nodes, and so in order to provide a machine with a peak capability of an exaflop one would have to deploy  $10^5$  nodes each performing at a computational rate of 10 teraflops or  $10^6$  nodes performing at a rate of 1 teraflop. In order to accomplish this, it is anticipated that each node will contain on the order of 1000 processing cores, each responsible for one or several parallel threads of control of a given program. Each core can ideally perform about  $10^9$  floating point operations and so, regardless of the number of nodes or cores, building an exascale machine in this way means exposing and managing  $10^9$  parallel threads of control. Such a level of parallelism has never been previously contemplated.

Another issue that leads to additional challenges when one considers computing at this scale is the amount of available memory and the ability of a processor to read and write data in such a way as to deliver it to the processor functional units at a rate sufficient to prevent idling of the processor. It will be seen that, owing to issues associated with cost and efficiency, it has not been possible to build memories for high performance computers of a size and speed that scale with the growth of the floating point throughput of the processor. It is already the case today that the flop to memory ratio (in terms of memory size) for a petascale machine is roughly 6 to 1 and, as can be seen from Table 3.1, this ratio is predicted to increase further in the absence of significant improvements in memory design.

Finally, the development of an exascale platform is ambitious because of the projected power requirements. Modern data centers typically provide about 20 megawatts of power. The building of an exascale system using today's technology would require much more than this as discussed further below.

#### **3.3** Overview of DOE Exascale Computing Initiative

In order to understand the needs for exascale computing, DOE and NNSA initiated in 2008 a series of community workshops on a number of relevant areas such as basic energy sciences, climate, materials, national security, etc. The goals of the workshops were to

- Identify forefront scientific challenges,

- Identify those problems that could be solved by high performance computing at the extreme scale,

- Describe how high-performance computing capabilities could address issues at the frontiers associated with the relevant scientific challenges,

- Provide researchers an opportunity to influence the development of high performance computing as it pertains to their areas of research, and

- Provide input for planning the development of a future high-performance computing capability to be directed by the Advanced Scientific Comput-

ing Research (ASCR) thrust of DOE's Office of Science and the Advanced Simulation and Computing (ASC) thrust of NNSA.

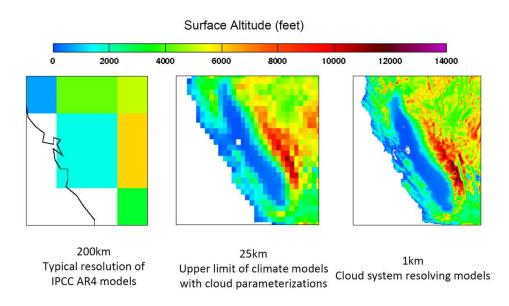

All of the scientific communities participating in the workshops identified a set of grand challenge problems that could profit from increased computing capability, and all welcomed the possibility of a thousand-fold increase in computing capability over current state of the art. For example, climate researchers identified the issue of integrated model development, that is, the need to simulate the oceans and particularly sea-ice and ocean circulation in interaction with the atmospheric dynamics that drive climate change. Researchers in Basic Energy Sciences identified issues associated with materials science such as computation of excited states and charge transport, the dynamics of strongly correlated systems, and the need to bridge disparate time and length scales in modeling the behavior of materials.

For NNSA, the main goal is the use of modern computation in support of stewardship of the nuclear stockpile. But within this broad area are fundamental issues such as the physics of nuclear fusion, the constitutive behavior of materials at high pressure and temperature, and the properties and chemistry of the actinide elements. All of these problems, which are key to ensuring confidence in the stockpile, require state of the art computational capability.

While all the relevant scientific communities could easily make the case that a factor of 1000 increase in capability would lead to increases in understanding, the challenge of achieving the level of parallelism as outlined above was typically not addressed. It was understood that significant changes in program and algorithm structure may be required in order to keep 1 billion threads of control active, and, indeed, the mapping of the computational patterns associated with various grand challenges is a research challenge in itself. DOE has therefore proposed the Exascale Computing Initiative that seeks to make investments in research and development that would lead to the introduction of an exascale platform operating within a power budget of roughly 20 Megawatts in the 2020 time frame.

#### 3.4 The 2008 DARPA Study

Several studies have already been carried out on the feasibility of exascale computing. Perhaps the most technically comprehensive of these studies is the 2008 Exascale Computing Study commissioned by the DARPA IPTO Division and the Air Force Office of Scientific Research (AFOSR). This study was led by Peter Kogge and was carried out by a group of experts in high performance computing [27].

The study examined the even more ambitious possibility of building an exascale system in the 2015 time frame and identified four major technical challenges:

- **Energy and power** A simple extrapolation of computing power requirements led to the conclusion that it would be impossible to achieve the deployment of an exascale platform using present day technology that would require only 20 Megawatts to operate by 2015. The main issue is the cost of moving data from processor to memory or processor to processor.

- **Memory and storage** The development of memory and storage technology follows a slower growth curve than that of processors with the result that memory capacity and speed have slowed significantly relative to processor capability. The projection to the exascale implies a system with a small fraction of memory capacity and bandwidth to computational capability.

- **Concurrency and locality** As mentioned above, it will be necessary to maintain something like a billion threads of control to achieve an exaflop. To do this,

it will also be necessary to make sure the requisite data is readily accessible to the computational units. Thus the data must be staged appropriately and the locality of the data must be maintained.

**Resiliency** Because an exascale system will involve on the order of 10<sup>5</sup> or more processors, hardware failures will occur more frequently than in systems of smaller size. The challenge of resiliency involves understanding the "life-time" of components and the assessment of the mean time to failure of the system. If such failures are frequent, it will be necessary to have strategies in place to route the computation around such failures so as to ensure the computations complete.

The 2008 DARPA study also emphasized the point that exascale computing is not only limited to the development of systems at the scale of a data center, but encompasses a more general program associated with the ability to further improve the performance of modern computing systems. The issues delineated by this study apply to all scales of computing. For example, there may be requirements in the future to develop at the smallest scale embedded or uniprocessor systems that use massive parallelism for a variety of tasks. This goal is known colloquially as the "teraflop laptop". A goal that is intermediate between an exaflop computer and a teraflop laptop is the development of a system that provides a petaflop of peak performance but with power requirements sufficiently modest that it could be housed in a small departmental computing facility. At present, petascale systems consume upwards of several megawatts and so this again represents an ambitious goal.

This study examines the evolution of technology four years since the DARPA report, but with an emphasis on how applications might be mapped on the evolving massively parallel architecture. This report also emphasizes some of the software challenges associated with programming exascale systems. Owing to the rather compressed time schedule associated with this study, it will not be possible to delve into these topics in as great a level of detail as the DARPA study. Remarkably, all of the observations made in the 2008 DARPA report as regards the state of computing technology remain valid today, and so interested readers should consult this study for a more complete technical assessment.

#### **3.5** Overview of the Report

In Section 4, we discuss in more detail the nature of the hardware challenges associated with achieving exascale capability. Our discussion will focus on the evolution of modern microprocessors. We also discuss the emerging gap between processor and memory performance. We assess some of the processing and memory requirements associated with applications relevant to the DOE/NNSA mission. We then discuss the resilience of modern multiprocessor systems. Finally, we examine some of the requirements for archival storage of the datasets that can potentially be generated.

In Section 5 we examine some of the application requirements associated with DOE/NNSA mission needs. It is not possible to cover this area completely, but the brief discussions provided in this section on requirements for applications such as climate simulation and combustion do highlight some key research requirements connected with some of the hardware limitations discussed in Section 4. We also discuss briefly the application requirements of the applications used by NNSA in stockpile stewardship. A more extended discussion of the way in which high performance computing is used in stockpile stewardship is available in a separate (classified) appendix (Appendix C).

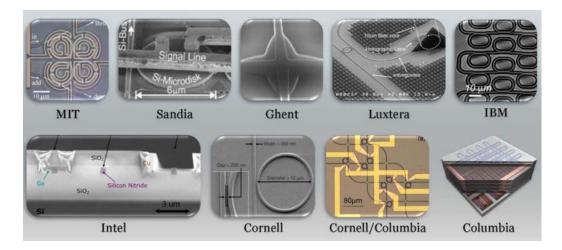

In Section 6, we discuss some technology developments aimed at overcoming some of the limitations associated with modern computing hardware. Again, we cannot be comprehensive in our coverage; among the areas discussed briefly are the development of new memory architecture and the use of photonics to aid in the efficient movement of data. We do discuss extensively the idea of using motifs of high performance computing as a way of understanding memory access patterns and communication overhead. These motifs (called "dwarfs") may be a useful organizing principle for both processor architecture and software abstractions aimed at optimizing performance.

In Section 7, we discuss some of the issues regarding design of software for HPC applications. Traditionally, this has been done using the message passing interface (MPI) in which messages to processors are constructed and transmission and reception of these messages is actively managed by the programmer. It is projected that, given the need to manage 1 billion threads, such an approach may eventually be unworkable. Some alternatives include the use of domain specific languages as well as the use of software auto-tuners to optimize the use of computational resources.

Finally, in Section 8, we conclude with some observations about co-design, the proposed process by which hardware designers and application developers engage in collaboration to influence future hardware design options. We then conclude with some recommendations.

## 4 HARDWARE CHALLENGES FOR EXASCALE COMPUTING

In this section, we describe some of the evolutionary changes in hardware for high performance computing (HPC). We then describe how recent hardware trends pose challenges associated with developing hardware for exascale computation.

#### 4.1 Evolution of Moore's Law

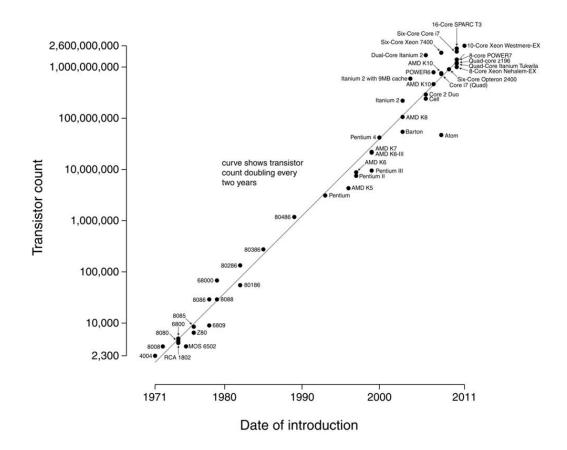

The exponential increase in computing capability has been enabled by two technological trends: Moore's law [31] and Dennard scaling [18]. Moore's law refers to the observation by Gordon Moore that the number of transistors on a microprocessor essentially doubles every 18–24 months. Shown in Figure 4-1 is the number of transistors associated with various processors manufactured between 1971 and 2011 demonstrating that this remarkable trend has held up for more than thirty years.

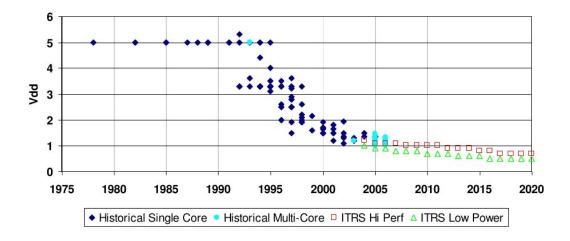

Dennard scaling refers to the ability to increase clock speed while decreasing processor feature size. It was realized by Dennard and others in 1995 that it was possible to reduce the feature size of a microprocessor by a factor of two (thus quadrupling the number of transistors on a chip) while also decreasing the processor voltage by a factor of two. This also had the salutary effect of reducing energy utilization by a factor of 8, since the energy scales with the capacitance of a device and the square of the voltage. It was then possible to double the speed of the processor by doubling the clock rate. The power consumption for the processor would remain the same as that for a processor with the lower clock rate and larger feature size, and so one would gain increased speed for the same processor

Figure 4-1: Number of transistors on a microprocessor as a function of time. The trend follows an exponential with a doubling time of roughly 24 months [31]

size. In this sense, it is possible to increase processor capability by a factor of 8 for the same total power. The evolution of processor voltages with time is shown in Figure 4-2. It can be seen that starting in 1995, rail voltages were decreased from about 5 volts over ten years down to about 1 volt or slightly below [27].

However, two physical issues eventually limited the ability to continue Dennard scaling. First, while total power is preserved as one halves the feature size and doubles the clock rate, the power density (power per unit area) increases by a factor of four. At a power density of 100 watt/cm<sup>2</sup>, thermal management of the processor via air cooling becomes increasingly difficult, and one must then resort to more exotic (and more expensive) cooling technologies. As a result, pro-

Figure 4-2: Evolution of processor voltages over time for a variety of microprocessor types. [27]

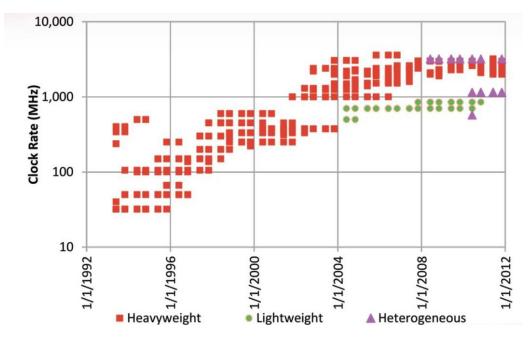

cessor manufacturers have not increased clock speeds past 3–6 gigahertz so as to preserve the use of air cooling. The evolution of processor clock rates is shown in Figure 4-3. As can be seen in the Figure, these have plateaued and are not expected to increase.

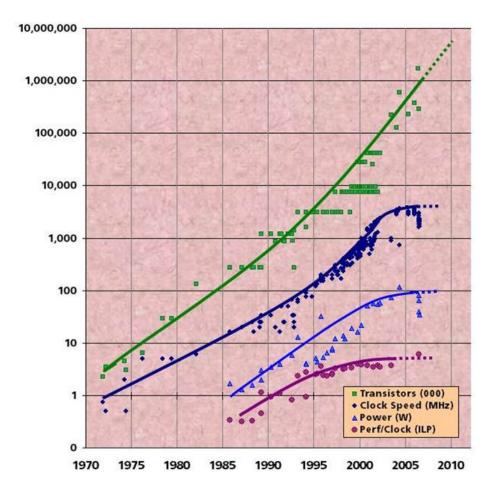

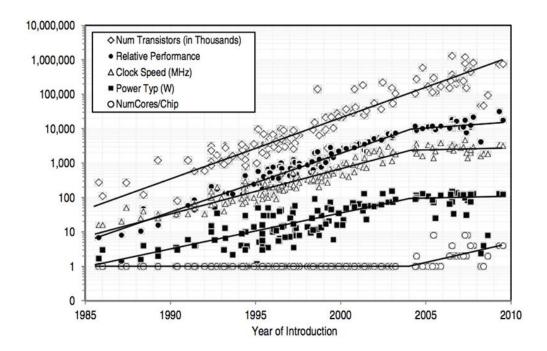

The second issue is associated with transistor leakage current. As a transistor shrinks in size, the oxide layer used to form the insulating layer also shrinks and this creates a larger sub-threshold leakage current, with the result that the switching characteristics of the transistor become unreliable. Because of this, as processor sizes have decreased, it has not been possible to further decrease power supply voltages. This trend is also shown in Figure 4-2. The overall effect of these trends is shown in Figure 4-4 which shows number of transistors, clock rate and power plotted together. There is clear knee in the clock and power curves owing to the issues described above. As a result of these issues, the overall instruction level parallelism of the processor has also flattened since it is now no longer possible to execute an instruction in a shorter time.

Figure 4-3: Evolution of clock rates over time [27]

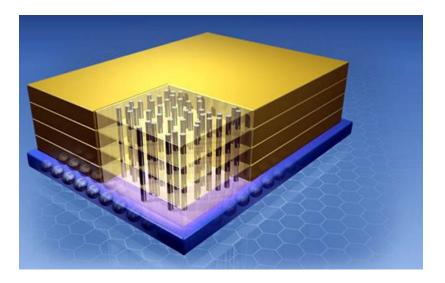

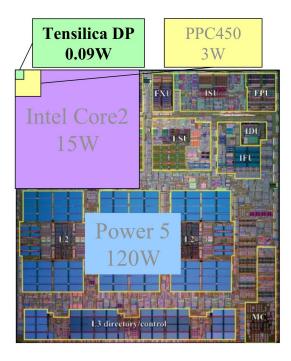

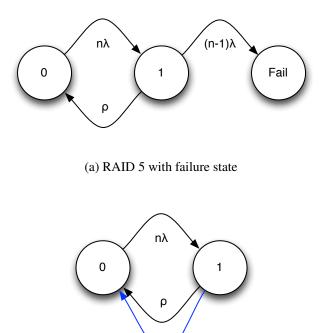

While it has been possible to continue increasing the number of transistors on a microprocessor as per Moore's law (as clearly borne out in Figure 4-1, as of 2004 this is now done in a different way. Processor manufacturers now lay out multiple processor elements on the chip as shown in Figure 4-5. These elements are called processor cores and can independently execute the full instruction set of the microprocessor. The cores can communicate via message passing over a network or through shared on-chip memory. Typically, the cores possess their own local memory hierarchy in the form of cache memory, but will also have to perform read and write operations to off-chip memory which is typically Dynamic Random Access Memory (DRAM). It is anticipated that in the absence of new processor technology, the future development of modern microprocessors will proceed through an increase in the number of cores. At present, the cores on mainstream microprocessors are identical, but it is envisioned that heterogeneous microprocessors will become available in which various cores perform specific functions such as I/O, security, etc.

Figure 4-4: Evolution of Moore's law. The top curve shows the total number of transistors on a microprocessor as a function of time and the trend continues to follow Moore's law. The second curve shows that clock speed has flattened. The third curve indicates that this was done to keep power levels low enough for cooling purposes. The final curve shows instruction level parallelism because clock speeds have flattened, instruction level parallelism has also flattened [34].

#### 4.2 Evolution of Memory Size and Memory Bandwidth

While the number of cores on each processor is increasing, the amount of total memory relative to the available computational capability is decreasing. This is a curious measure, but relates to how much memory is available for a given performance level. In the past, memory technology scaled in a similar way to processor capability, and so it was possible to provision one byte or more of avail-

Figure 4-5: A view of Moore's law showing evolution of the number of cores on a processor (bottom curve) [21].

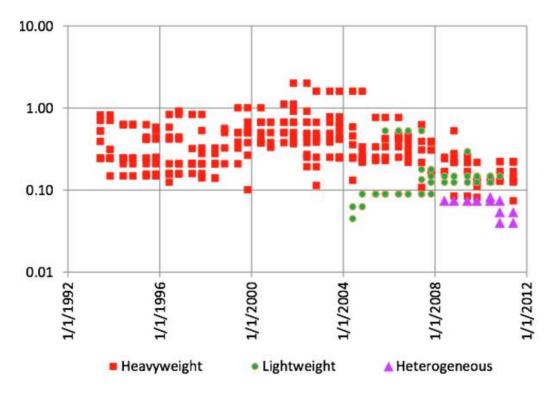

able memory for each flop of processing capability. At around the same time as the transition to multi-core architecture, the ratio of available bytes to flops began decreasing. This is shown in Figure 4-6. Prior to 2004, the memory size was comparable to the number of flops and the ratio of bytes to floating point capability as measured in flops hovered around and in some cases exceeded one. As of 2004, the ratio dropped (note that the figure uses a log scale) and is now edging close to 0.1 for heterogeneous (i.e. multi-core) processor architectures. If this trend persists (and with current technology it is expected to worsen), it will have an important impact on the type of applications which can be run on machines that use traditional DRAM. We discuss this further in Section 5.

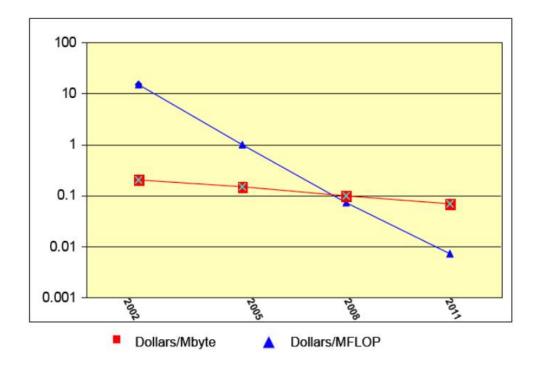

Memory capacity using traditional DRAM technology turns out to be a matter of cost. As shown in Figure 4-7, the cost of memory has not been decreasing as rapidly as the cost of floating point performance. From the point of view of

Figure 4-6: Evolution of the ratio of total memory capacity to floating point performance. The vertical axis units are bytes/flop. Prior to 2004 it was possible to provision 1 byte per flop. Recently this has dropped to less that 0.10 byte per flop [27].

the amount of memory resident on single processor, enormous advances have still been made. Today, DRAM costs about \$5 per gigabyte and so the cost of provisioning say a 32 gigabyte memory for a personal computer is not prohibitive. However, if one desires a ratio of one byte per flop for an exascale machine, this will require an exabyte of memory and at today's costs this is will be \$5 B. It is anticipated that while memory costs will decrease, extrapolations using the JEDEC memory roadmap still indicate a cost of perhaps \$1 per gigabyte or more in the 2020 time-frame [53]. As a result, even in 2020 an exabyte of memory will cost on the order of \$1B. Typical budgets for DOE/NNSA high end computer systems are on the order of \$100–200M, and so using current memory technology, it will only be possible to provision roughly 200 petabytes of memory at best. More

Figure 4-7: Evolution of memory cost as a function of time. Also shown is the evolution of floating point cost for comparison. It is seen that floating point costs have decreased far more rapidly [48].

realistically, a memory size of 50 petabytes or so is envisioned.

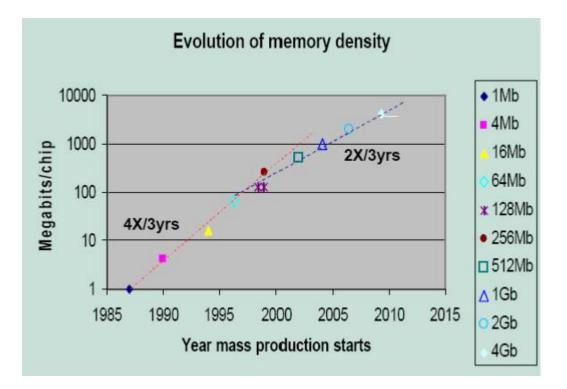

One might argue that improvements in technology will lead to higher memory densities and so the 4 GB DRAM of today would evolve into the 1 Terabyte memory of 2020. Indeed, memory density has increased over time as shown in Figure 4-8. However, the rate of increase of memory density has never been as rapid as that of Moore's law for the number of transistors on a processor. As shown in the Figure, memory density increased at a rate of 1.33 MBit/chip/year from 1987 through about the year 2000. Afterwards however, the rate slowed to 0.66 Mbit/chip/year. Today, it is possible to purchase 4Gb on one memory chip. If current rates of increase hold, it will not be possible to have a terabit memory chip until perhaps 2034.

Figure 4-8: Evolution of memory density as a function of time [48]

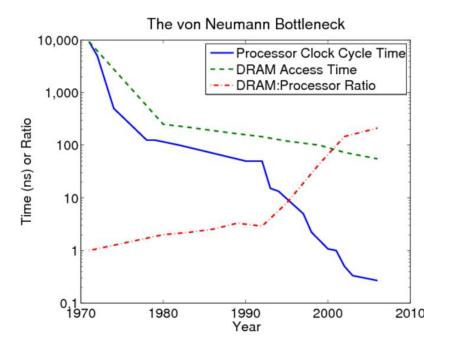

Memory bandwidth, or the ability to move data from memory to processor registers is also a key concern. The memory system associated with a modern microprocessor is provisioned hierarchically. For processors, one wants rapid instruction execution, while for a memory one wants high density to maximize data available to the processor. As a result, as processors have become more capable and can execute instructions more rapidly, a performance gap has developed in that the access times for memory, while decreasing, have not decreased as rapidly as processor cycle times. This is shown in Figure 4-9. In 1970 the access times for DRAM and processor cycle times were comparable, but by 1990, as chip designers discovered the benefits of decreasing feature size, lowering voltages, and increasing clock speed, processor cycle times dropped dramatically. As a result, the ratio of DRAM access time to processor cycle time began to increase. By 2007, the ratio increased to several hundred to one. Processor designers call this

Figure 4-9: An illustration of the von Neumann bottleneck. Processor clock cycle time (blue curve) is plotted over time and compared with DRAM access time (green dashed curve). The ratio of the two is also shown (red dashed curve). Note that over time the ratio has increased [32].

problem the "memory wall" or the "von Neumann bottleneck", since it was von Neumann who first developed the idea of an independent processor that retrieved its instructions and data from a separate memory.

Processor designers addressed this issue by designing hierarchical memories to mask the memory latency. In addition to the main memory in the form of DRAM, modern processors possess memory caches which can store data from DRAM so that future requests for that data are readily available. Cache memories located on-chip are typically built from static RAM or SRAM. This type of memory is constructed from transistors and is very fast, but it has the lowest data density. It is also more susceptible to radiation induced upsets and so must also be designed with error correction logic. In contrast, DRAM cells use capacitors for storage and transistors to move the charge onto an accessed bit-line. This results in a very dense memory, but compromises must be made here too. For example, memory access produces not just one desired word, but a whole line of memory which can be a thousand or more words. For these and other reasons, memory access times from DRAM have not decreased as rapidly. This is not to say that one could not build a faster DRAM. Indeed there are several promising approaches such as embedding the DRAM in the processor, or altering the DRAM core to tailor the amount of data that is retrieved. However, all these concepts impose a penalty on the die size, and, typically, vendors have not embraced these ideas because providing high memory density is the dominant driver in commodity computers.

Given the hierarchical nature of processor memory, it is preferable to find a piece of required data in the cache where it can be accessed more rapidly. Data is transferred to cache from main memory in blocks of fixed size called cache lines. When the processor needs to read or write a location in main memory, it first checks to see if the memory address or one associated with the cache line is available. If the data is present this is called a cache hit. If not, it is a cache miss; a new entry is allocated in the cache, and the required data is read in from main memory. The proportion of successful cache accesses is called the cache hit rate, and this is a measure of effectiveness for the way in which a particular algorithm utilizes the processor. Processors use caches for both instruction, data and also address translation.

Cache misses are characterized by how the miss occurs:

**Compulsory misses** These occur whenever a new piece of memory must be referenced. The size of the cache or the way the cached data is associated with main memory will make no difference here. An increased cache block size can help in this case, as there will then be a higher probability the required data is cached, but this is algorithm dependent. The best approach is to prefetch the data into the cache. This requires active management of the cache which is typically left to the compiler. Even prefetching has limits if a large amount of data is required.

- **Capacity misses** Capacity misses occur because the cache is simply too small. If one maps the capacity miss rate vs the cache size one can get a feel for the temporal locality of a piece of data. Note that modern caches are typically always full and so reading a new line requires evicting an old line of data.

- **Conflict misses** This is a miss that occurred because the required data was already evicted from the cache. Some of this can also be dealt with through the provision of larger caches, but because this entails a penalty in terms of silicon area and performance relative to the provision of functional units, it is not generally cost effective to increase the cache size.

A cache miss from an instruction cache will cause the most delay as the thread of execution must halt until the instruction is retrieved. A cache miss from a data cache may not be as detrimental as instructions that do not depend on the needed data can be executed instead until the required data arrives. This "out of order" execution strategy was successful in several processors but is now considered to be of limited utility because processor speeds have grown faster then memory access speeds.

#### 4.3 Memory Access Patterns of DOE/NNSA Applications

From the discussion above, it can be seen that the overall performance of a given application will depend on the amount of memory required to perform the operations associated with a given algorithm as well as the access pattern associated

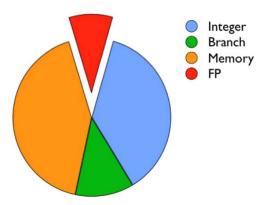

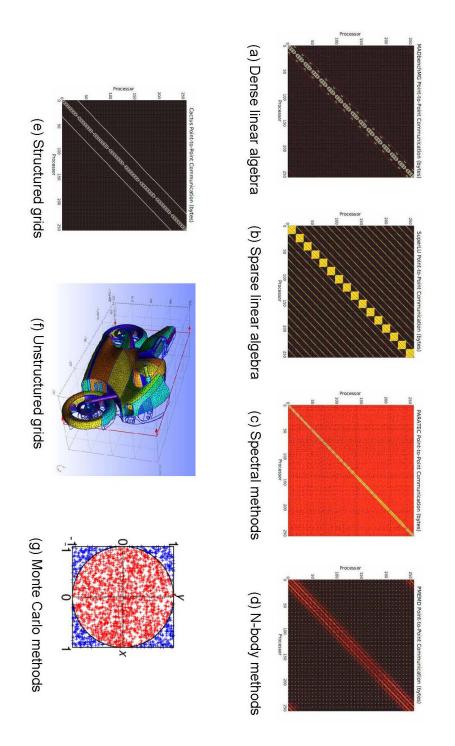

Figure 4-10: A breakdown of the types of computational operations required for DOE/NNSA applications [32].

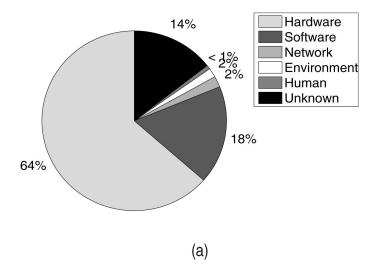

with that memory. As a first step, it is important to understand what percentage of operations are related to memory access in a given DOE/NNSA application. The suite of possible applications is of course very large, but a representative sample has been studied as briefed to JASON in [32]. The percentage of various types of operations executed in these codes has been examined and is shown in Figure 4-10. DOE/NNSA applications are generally viewed as floating point intensive, as a large part of the workload pertains to the numerical solution of partial differential equations (PDEs). Remarkably, the number of floating point operations in the execution of this particular suite of DOE/NNSA applications is only approximately 10% of the total. Memory operations for the remaining 10%. Of the integer operations which account for 40% of the total number of instructions, roughly 40% of these arise from the calculation of the addresses of floating point data. Only 10% of integer instructions are used for actual integer computation.

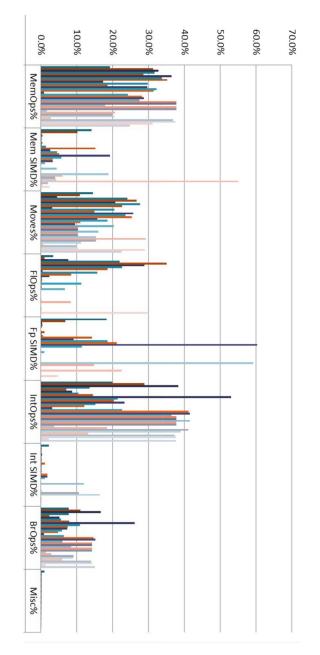

A much more detailed look is provided by the (very busy) graph shown in Figure 4-11 as developed by J. Vetter and his colleagues [49]. In this Figure, the

Figure 4-11: Instruction mix for DOE/NNSA applications [49]

Figure 4-12: Histograms of instruction mix for DOE/NNSA applications. [49]

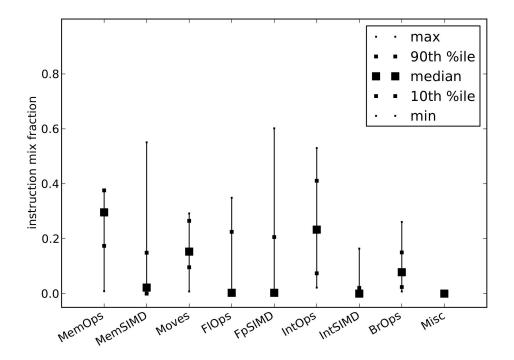

resource attributes of a number of applications relevant to the DOE/NNSA workload are plotted as percentages. Overall, these statistics validate the distribution of operations shown in Figure 4-10. As can be seen, roughly 35% of the operations of most of the codes are memory operations. While some of codes do exhibit a significant percentage of floating point intensity, the majority do not. The strong floating point peaks originate from codes such as HPL which implements the high performance LINPACK benchmark [36]. This code performs an LU decomposition of a random matrix, and is tuned to minimize memory references while maximizing floating point throughput.

Another view of this distribution of memory vs. floating point operations is seen in Figure 4-12. Here we plot the results of memory operations, floating point operations etc. by examining the distribution of the percentages for each performance attribute that has been recorded in [49]. As can be seen, the median fraction for memory operations is at roughly 35%, indicating half of the surveyed applications exhibit memory access intensities at 35% or more. The situation for floating point operations is even more striking. The median for both floating point operations and floating point single instruction multiple data (SIMD) operations is quite low. Thus the applications associated with the DOE/NNSA workload require significant memory references relative to floating point and so their performance is very sensitive to the characteristics of the memory system such as memory bandwidth. This occurs for several reasons. Compilers are not always able to optimize floating point throughput without assistance from the programmer. In addition work is required on the organization of the data flow of the applications so as to understand if alternate approaches can lead to better performance. We discuss this further in Section 4.4.

Because of the hierarchical nature of the memory system on a modern microprocessor, there is a significant performance penalty if a required piece of data is not available in the various caches of the microprocessor. In this case, the data, in the form of a cache line, must be requested from main memory, and if no other productive work can be performed while this access takes place, the processor will stall. An interesting study of this issue was undertaken by Murphy et al. [33], who examined the the implications of the working set size on the design of supercomputer memory hierarchies. In particular, they compared the working set sizes of the applications in the Standard Performance Evaluation Corporation (SPEC) floating point (FP) benchmark suite to that of a set of key DOE/NNSA applications run at Sandia National Laboratories. The type of computations performed by these applications are quite typical of the workload associated with DOE Science applications as well as NNSA stewardship applications. They include

- LAMPPS a classical molecular dynamics code designed to simulate atomic or molecular systems,

- CTH a multi-material large deformation shock physics code used at Sandia to perform simulations of high strain rate mechanics, and

- sPPM a simplified benchmark code that solves gas dynamics problems in 3D by means of the Piecewise Parabolic Method [11].

The methodology used in this study is to extract an instruction stream of about four billion instructions from each of these codes. Care was taken to ensure that the instructions were associated with the core computational aspects of each of the applications. To determine the working set miss rate of a given application, the authors simulated a 128 MB fully associative cache using a least recently used (LRU) cache eviction strategy. During each load or store operation in the instruction stream, the cache list is searched for the requested word address. If the entry is found (a hit) a hit counter for that block is incremented. That entry is then promoted to the head of the cache list so that it becomes the most recently used item. By varying the working set size, that is, the list of cache entries, it is possible to examine the memory requirements for a given application. Note that this approach measures what is called the temporal working set size miss rate; miss rates here refers only to temporal locality as opposed to spatial locality. It is possible that more sophisticated caching or prefetch schemes that take spatial locality into account could reduce miss rates. As the working set size increases, the probability that the required datum will be found increases, and the miss rate decreases. But it will eventually plateau at a level where further increases in working set size (up to 128 million blocks) will not reduce the miss rate, and when this point is reached one is measuring the compulsory miss rate. In this case, the required data for this maximum working set size must be fetched from main memory.

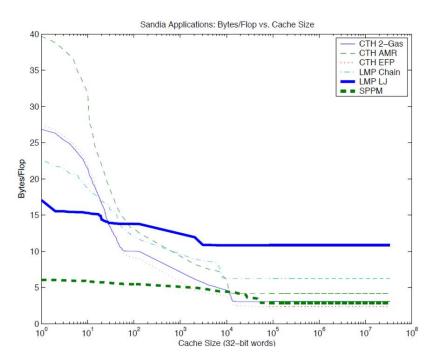

Figure 4-13: A measure of the bytes required per flop for a variety of Sandia applications. Note that the vertical axis label of bytes/flop now refers to required memory bandwidth [33].

Once the miss rate and flop rate are measured, it is possible to infer a memory bandwidth requirement by dividing the cache miss rate by the number of flops required to perform a given computation. This byte to flop ratio<sup>1</sup> is indicative of the memory bandwidth required. For example, if this rate is less than one, then less than one byte per flop must be accessed from main memory. This is a favorable situation for a modern microprocessor, because it indicates the computation has high arithmetic intensity; there is significant use (and reuse) of the bytes accessed from memory into the caches. In this case, we can expect the floating point units to perform at near optimum rate. On the other hand, if this ratio is greater than one then it implies that the computation will be limited by the bandwidth associated with access from main memory. The results for the Sandia applications are shown in Figure 4-13. It can be seen that even with a cache size of 128M words, the byte

<sup>&</sup>lt;sup>1</sup>Not to be confused with the memory capacity to flop ratio discussed earlier.

to flop ratio never goes below one. For applications that perform regular memory accesses like sPPM or CTH, we see that, eventually, we hit a plateau of 3-4 bytes per flop. But this only happens at a cache size of 100 kB or so. Modern level 1 caches are typically 64 kBytes in size. Level 2 caches are generally bigger, up to several megabytes. On a typical multi-core processor, however, only a level 1 cache is available to each core. Access to caches at level 2 and above takes place via a shared memory bus.

We emphasize that this analysis is not definitive for two reasons. First, it does not completely take into account the role of prefetching of data from memory to a level 2 cache. Secondly, the binaries that are run in this analysis are not handoptimized, and it may be possible to improve this byte to flop ratio by applying techniques to manage cache affinity. The authors in reference [33] also applied this analysis to the SPEC-FP benchmark and showed that the byte/flop ratios for these applications are smaller than those for the Sandia suite. One can conclude, therefore, that the DOE/NNSA workload may require greater memory bandwidth than conventional floating point intensive applications, but this requires further systematic assessment. A more quantitative view of the memory bandwidth issues is presented in the next section.

# 4.4 The Roof-Line Model

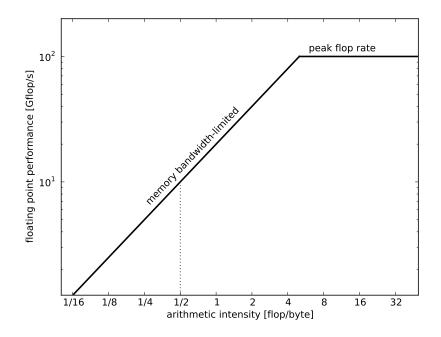

A useful framework for understanding the performance of scientific applications on a given hardware platform is the "roof-line" model [54]. The essence of this idea is that applications with sufficiently high byte to flop ratios, as discussed above, will be limited in the floating point rate they achieve by the memory bandwidth of the system. Figure 4-14 shows the roof-line model for a generic computer that is characteristic of today's commodity platforms, with a peak floating point

Figure 4-14: Roof-line model for a generic 2012 commodity computer, with 100 Gflop/sec peak floating point performance, and 20 Gbyte/sec memory bandwidth. The solid curve represents the maximum achievable floating point performance of an application as a function of its arithmetic intensity (flops-to-byte ratio). Below 5 flop/byte, an application is memory bandwidth-limited, as shown by the sloped line. Above 5 flop/byte, an application can achieve the peak floating point performance provided by the CPU. The dashed line shows a hypothetical scientific application at an arithmetic intensity of 0.5.

capability of 100 Gflop/sec, and a peak memory bandwidth (between DRAM and CPU) of 20 GB/sec. Plotted in the figure is the maximum achievable floating point performance as a function of the arithmetic intensity (flop-to-byte ratio, where "byte" refers to a byte of memory read from DRAM) of an application running on this hardware. <sup>2</sup> At high arithmetic intensity (> 5), there is sufficient memory bandwidth to keep the processor fed, so the peak floating point rate of the CPU is achievable. At low arithmetic intensity (< 5) there is not enough memory bandwidth to keep the floating point units busy, so the maximum achievable floating

$<sup>^{2}</sup>$ Note, the following discussion uses the metric of flops to bytes rather than bytes to flop. The former is the right metric to use when there is good reuse of cache data.

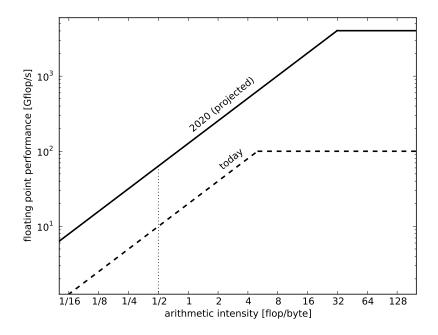

Figure 4-15: Roofline model for a generic commodity computer in 2020 (solid line) and 2012 (dashed line). Memory bandwidth is assumed to double every 3 years, while floating point performance is assumed to double every 1.5 years. Note that the ridge point moves from 5 flop/byte to 32 flop/byte.

point rate is limited by the memory bandwidth, as indicated by the sloped line. The point on this figure where the memory bandwidth-limited floating point rate meets the peak floating point rate is known as the "ridge point," and occurs at an arithmetic intensity of 5 for this generic processor. In other words, to reach peak floating point performance on this hardware requires an application that can perform 5 floating point operations for every byte of memory read from DRAM. Scientific applications of interest to DOE or NNSA span a range in arithmetic intensity, but rarely have intensities above 1 [33]. The optimistic value of 0.5 is shown in the figure as a vertical line. For such an application on this hardware, the maximum achievable floating point performance of the CPU of 100 Gflop/sec.

There is every indication that the trend of CPU performance doubling every 18 months (via Moore's Law) [31] will continue; as indicated previously, this performance increase is realized today by an increase in the number of processor cores instead of an increase in the performance of an individual core, but this detail is not relevant to the current discussion. The trend for memory bandwidth improvement, however, has been the subject of much less focus. Over the past decade, memory bandwidth to CPU has doubled approximately every 3 years [38], and current indications are that the growth rate will decrease absent new developments.

Making the optimistic assumption that memory bandwidth trends will continue (at a doubling every 3 years), and assuming that CPU performance will continue to follow Moore's Law, we plot in Figure 4-15 the roof-line model for a commodity system in 2020. For reference, we include the roof-line model for today's hardware as the dashed line. By 2020, CPU performance gains will have outpaced memory bandwidth gains to such a degree that to reach peak floating point performance on our representative system will require something like 32 flops per byte in arithmetic intensity! Our reference application with an arithmetic intensity of 0.5 will reach a mere 63 Gflop/sec in floating point performance on a CPU capable of a peak floating point rate of 4 teraflop/sec. This corresponds to an efficiency of only 1.5%!

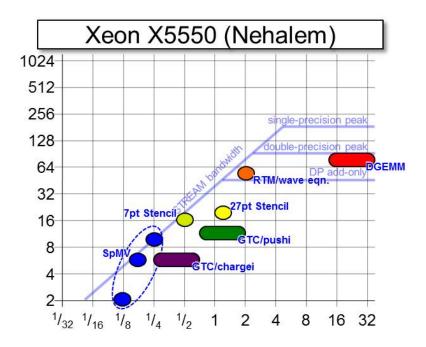

Yelick and her colleagues at Berkeley have applied the roof-line model to DOE/NNSA applications [57]. In Figure 4-16, we show the roof-line curve for the Intel Xeon 550, a commercial processor used in workstations and servers. The Xeon processor has a peak speed of about 256 gigaflops per second using single precision arithmetic. The memory system for this processor is such that it requires an arithmetic intensity of about 4 flops per byte in order to realize this peak per-

Figure 4-16: Roofline results for the Xeon processor [57].

formance. The colored regions correspond to several types of applications that use the same computational patterns as DOE/NNSA applications. For example "SpMV" in the Figure stands for a sparse matrix vector multiply, an operation that is relevant for example to finite element analyses. As can be seen, the efficiency for this pattern is quite low, ranging from 2 gigaflops at the low end to 8 gigaflops at the high end; the memory bandwidth achieved is quite low, with a flops to byte ratio less than one in all cases. This is to be contrasted with the DGEMM application corresponding to a full matrix-matrix multiply. This corresponds to a different computational pattern, and the algorithms for matrix multiplication of full matrices allow for significant reuse of cached data. This type of calculation is often used to characterize the peak floating point performance of a modern processor. The other colored regions represent applications that have computational patterns that do not perform optimally given the roof-line limits, presumably because traditional memory caching strategies are inadequate.

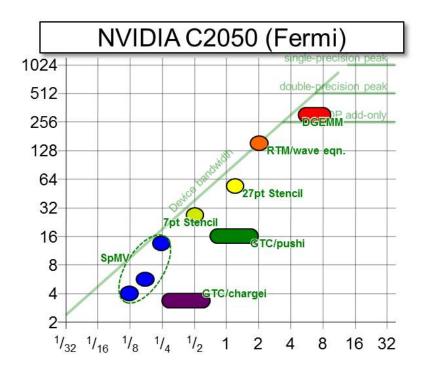

Figure 4-17: Roof-line results for the Nvidia Fermi processor [57].

In Figure 4-17 we show the same roof-line curve but for a modern graphics processing unit (GPU), the NVIDIA Fermi C2050. A GPU can provide significant performance improvements over a traditional processor provided the flop to byte ratio is sufficiently high. For example, the dense matrix-matrix multiply is accelerated by almost a factor of four over the Xeon processor. In contrast, applications like the sparse matrix-vector multiple do not show appreciable speed-up. Again, the issue is to be able to either cache memory effectively or apply an application-specific prefetching strategy that can hide the latency of the required memory accesses.

Extrapolating current trends, it is clear that commodity hardware is changing in a way that will continually reduce the efficiency of existing science applications. The question, of course, is "What can be done?". The roof-line model shown in Figure 4-15 suggests possible solutions. Since processors are currently limited in terms of memory bandwidth, and will certainly be so in 2020, one could imagine attempting to influence vendors to design higher bandwidth CPU– DRAM interconnects. One difficulty faced here is that memory bandwidth is approximately proportional to the number of leads coming from the CPU package, and we are currently facing physical constraints in increasing this number. Another difficulty with increasing memory bandwidth, as we discuss below, is that the energy cost to move data (the dominant energy cost in scientific calculations) at exascale may greatly exceed a reasonable power budget.

Another possible solution suggested by Figure 4-15 is to increase the arithmetic intensity of DOE/NNSA science applications. This can be achieved in one of two ways. First, by optimizing and tuning a code, one can sometimes increase the flops-to-byte ratio without changing the underlying algorithm. This typically takes the form of structuring memory accesses to increase the cache hit rate, and usually leads to modest increases in arithmetic intensity, although, to our knowledge, a thorough study of the potential for this approach has not been undertaken for DOE/NNSA applications. In Section 7, we describe some techniques for automating and simplifying this process. The second method for increasing the flops-to-byte ratio is to modify the underlying algorithm itself. This may be possible in some cases, but the path forward is not clear for all applications associated with the DOE/NNSA workload. This is clearly a research priority. It is interesting to note that the development of capable hardware can make it possible to use algorithms which were previously not thought to be suitable. For example, while the idea of the fast Fourier transform (FFT) was understood some time ago (possibly by Gauss), it was only the invention of the digital computer which made it a revolutionary advance as pointed out by Cooley and Tukey [13].

Although our discussion of hardware so far has been kept rather simplified, it should still be clear that the scaling trends do not favor scientific applications if the flops to byte ratios are indeed as low as indicated in the previous section.

## 4.5 Energy Costs of Computation

An additional major technical issue in realizing exascale computing is the cost of energy for computation. It is not hard to see that energy cost is a potentially significant issue. For example, the IBM BG/P computer recently installed at the Lawrence Livermore Laboratory achieves a LINPACK benchmark speed of 16 petaflops and uses roughly 8 megawatts of power. If one envisions achieving an exaflop by simply scaling up this technology, such a computer would require 400 megawatts to operate. At current rates for power this would cost \$400M per year assuming it were possible to deliver 400 megawatts to the data center housing the computer.

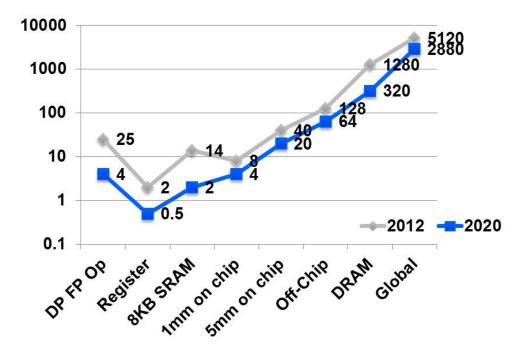

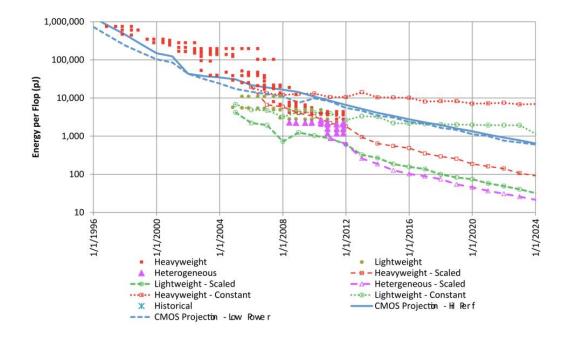

Shown in Figure 4-18 are the energy costs of various basic operations as measured in picoJoules on a 64 bit word. The gray curve represents the energy costs today. The blue curve represents projected energy costs for these operations in 2020. For example, a double precision floating point operation today requires about 25 pJ of energy. By 2020, as feature sizes for microprocessors shrink further, it is expected that such an operation will require only 4 pJ. The costs for register access are even less, and the costs for accessing an 8 kB SRAM are comparable. This is because all such operations take place close to the functional units of the processor, and as mentioned earlier, SRAM memory is built from transistors and is designed for rapid access, but has low density relative to DRAM.

Figure 4-18: Energy costs for computational operations. Vertical axis labels denote picoJoules. All costs are for operations on a 64 bit word [26].

Other operations that require communication over the processor must factor in the cost of signaling plus the cost of performing the operation. For example to communicate a 64 bit word over a distance of 1 mm across the chip costs roughly 8 pJ per mm of distance. This is due to the resistance that must be overcome in performing the signaling. Note too that while a factor of six reduction in energy use is projected for floating point operations by 2020, a more modest factor of two improvement is projected for communication across the chip.

Finally, there is a very large disparity between the energy costs of floating point computation and off-chip memory access. Today, a DRAM access for 64 bits requires 1.2 nJ and this may decrease by a factor of 4 to 320 pJ by 2020. The ratio of energy costs between memory access and floating point today is about 50 to 1 today but is projected to increase to 80 to 1 by 2020.

While the energy costs of individual operations seem quite modest, they become substantial when one contemplates building an exascale computer. A power utilization rate of 1 pJ per second translates into a utilization rate of 1 MW per second if one simply scales up to the exascale. Because the power budget for most modern data-centers is on the order of 20 MW the provision of hardware resources for an exascale machine is constrained not only by technological issues but also by energy utilization.

#### **4.6** Memory Bandwidth and Energy

The memory bandwidth issue is largely one of energy, and, to a lesser extent, pin constraints. Accessing DRAM today requires about 30 pJ/bit, so a 200 GB/sec (1.6 Tb/sec) memory system on a single GPU node consumes about 50 W. This is divided three ways between row activation (bit-line energy), column access (on-chip communication from the sense amps to the pins of the DRAM), and I/O energy (off-chip communication).

There are techniques that can reduce all three components of energy. Row activation energy is high because each row access reads a very large (8K-bit) page. Reducing the page size will linearly reduce this component of energy. For example, using a 256 B page size will save a factor of 32 on row activation with little downside. Column access energy can be reduced by more efficient on-chip communication. On-chip communication energy is currently about 200 fJ/bit/mm and circuits have been demonstrated operating at 20 pJ/bit/mm. Finally off-chip communication using the single transmission line (STL) signaling standard used in DRAM takes about 20 pJ/bit (2/3 of the total energy) and signaling systems with 1-2 pJ/bit have been demonstrated. Based on expected improvements, one can expect total access energy for commodity memory to drop to the 5-10 pJ/bit

| Floating<br>point<br>capability<br>(flops) | Memory<br>capacity<br>(bytes) | Required<br>Memory<br>bandwidth<br>(bytes/flop) | Power<br>(2012) | Power<br>(2020) | Cost for<br>Memory<br>(2020) in<br>\$ |

|--------------------------------------------|-------------------------------|-------------------------------------------------|-----------------|-----------------|---------------------------------------|

| <b>10</b> <sup>18</sup>                    | 0                             | N/A                                             | 25 MW           | 4MW             | \$0                                   |

| <b>10</b> <sup>18</sup>                    | <b>10</b> <sup>18</sup>       | 1                                               | 160 MW          | 44MW            | \$1B                                  |

| <b>10</b> <sup>18</sup>                    | <b>10</b> <sup>18</sup>       | 0.5                                             |                 | 24MW            | \$1B                                  |

| <b>10</b> <sup>18</sup>                    | <b>10</b> <sup>17</sup>       | 1                                               |                 | 8MW             | \$100M                                |

| <b>10</b> <sup>18</sup>                    | <b>10</b> <sup>17</sup>       | 2.0                                             |                 | 12MW            | \$100M                                |

| <b>10</b> <sup>18</sup>                    | <b>10</b> <sup>17</sup>       | 3.0                                             |                 | 20MW            | \$100M                                |

| 10 <sup>18</sup>                           | <b>10</b> <sup>17</sup>       | 5.0                                             |                 | 24MW            | \$100M                                |

Table 4.2: Some point designs for an exascale computer. These estimates use the energy costs of DRAM access and floating point computation and assume the processing of the full memory capacity of the machine.

range by 2020.

With today's DRAM costs and a power budget of 50–75 W for DRAM access, one is limited to 200–300 GB/sec bandwidth. With a drop to 10 pJ/bit in 2020 the energy limit on bandwidth will be 600–900 GB/sec. Pin bandwidth is also a limiter here. One can place 512-1K channels per chip and run them up to 20Gb/sec (perhaps 40Gb/sec by 2020) so the pin bandwidth limit is 1.2–2.4 TB/sec today and is expected to be 2.4–4.8 TB/sec by 2020. With both today's technology and expected scaling, energy is a bigger limiter than pin bandwidth. Also, one can overcome the pin limit by splitting a processing chip into several smaller chips. To first approximation, the pin bandwidth per chip, which is limited by the escape pattern, under the package remains constant.

#### 4.7 Some Point Designs for Exascale Computers

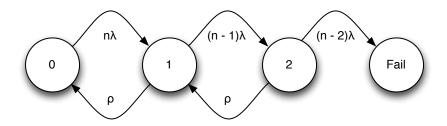

Using the energy and cost estimates discussed above, it is possible to make rough estimates of the power requirements for exascale platforms. Table 4.2 uses the memory cost figures in Section 4.2 and the energy figures in the previous section to compute rough power costs and memory costs for various configurations of an exascale system.